ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

Synopsys, Samsung Foundry Deepen Collaboration

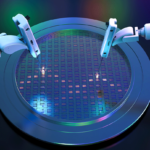

Synopsys, Inc. and Samsung Foundry are deepening their collaboration to help chipmakers accelerate the design of 2.5D and 3D multi-die systems on Samsung’s most advanced process technologies. The collaboration addresses key requirements of multi-die systems for intense computing applications including high-performance computing, AI, automotive and mobile. By providing an unmatched combination of certified EDA reference flows including Synopsys 3DIC Compiler and UCIe IP for die-to-die connectivity, mutual customers can accelerate the development of multi-die systems on Samsung Foundry’s 5nm, 4nm and 3nm processes and using I-Cube and X-Cube technologies.

“Semiconductor designers are dealing with new levels of complexity as they develop high-performance systems for data-intensive applications on the most advanced geometries,” said Sanjay Bali, vice president of Strategy and Product Management for the EDA Group at Synopsys. “The strong collaboration between Synopsys and Samsung on the development of UCIe IP and certified EDA flows addresses emerging requirements for multi-die systems utilizing Samsung’s advanced process nodes and multi-die integration flow.”

Meets Stringent Performance

By integrating multiple dies on different nodes into a single package, using die-to-die interconnects such as UCIe and advanced fan-out wafer-level packaging, designers can meet their stringent performance and time-to-market requirements for compute-intensive designs. In addition, the Synopsys Multi-Die Solution supports Samsung Foundries’ I-Cube and X-Cube technologies, a comprehensive family of 2.5 and 3D silicon stacking and advanced packaging technologies. The flexibility of multi-die systems provides an efficient way to deliver task-optimized applications such as self-driving vehicles and high-performance computing.

“Compute-intensive workloads for our data-driven world require customers to meet ambitious power, performance and area targets for even the most demanding process technologies,” said Sangyun Kim, vice president of Foundry Design Technology Team at Samsung Electronics. “Together, Synopsys and Samsung Foundry are optimizing multi-die designs, from early to full system implementation and signoff analysis to IP readiness. Our close collaboration results in advanced productivity solutions that reduce turnaround time and costs for our mutual customers.”

Synopsys 3DIC Compiler supports Samsung’s new 3D CODE standard and is part of the broader Synopsys Digital Design Family and, combined with Synopsys Fusion Compiler™ and AI-driven design enabled by Synopsys.ai suite of technologies, enables unified system-on-chip (SoC) to multi-die system co-optimization. Ansys® Redhawk-SC Electrothermal™ multi-physics technology is tightly integrated with Synopsys 3DIC Compiler to address the power and thermal signoff for multi-die systems.

To streamline development while lowering integration risk, Synopsys is collaborating with Samsung to develop IP for multi-die systems, including UCIe IP, on Samsung Foundry’s most advanced process technologies.