ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

New ASE VIPack™ Caters Chiplet Integration for AI Era

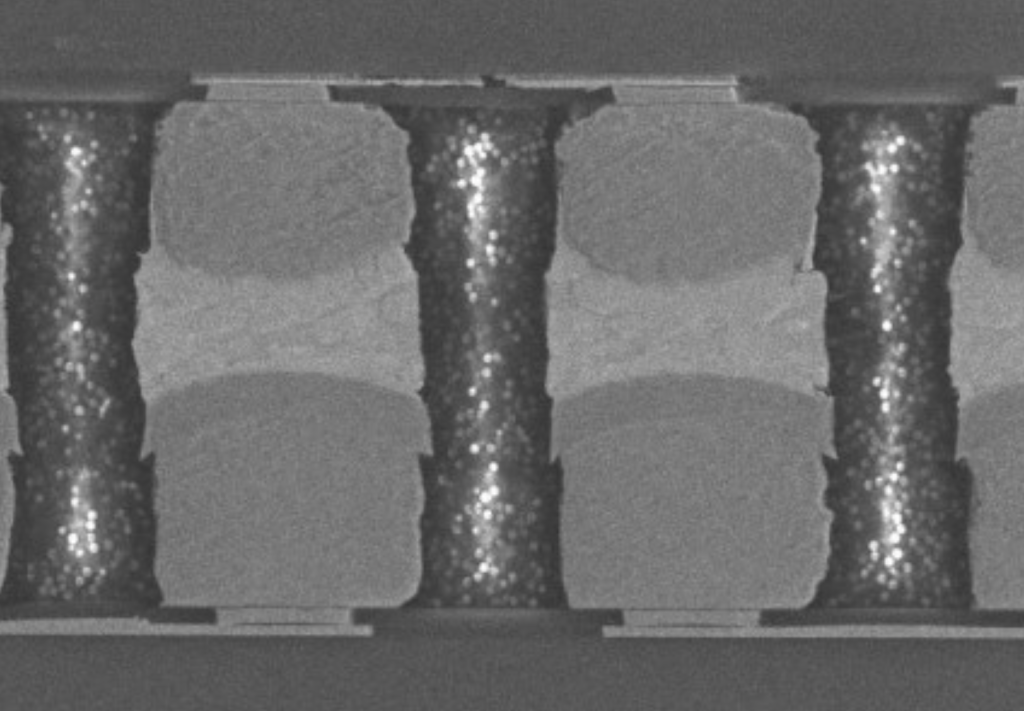

Advanced Semiconductor Engineering, Inc. (ASE) has extended its advanced interconnect technology under the VIPack™ platform to meet the accelerating demand for complex chiplet integration for artificial intelligence (AI) applications. Mainly, this interconnect extension advances roadmap capabilities from a chip-on-wafer interconnect pitch of 40µm to 20µm through advanced microbump technology. Such new interconnect solutions are crucial for architects seeking to accomplish creativity and scale across 2D, or side-by-side, solutions as well as newer vertically integrated solutions, such as 2.5D and 3D packaging capabilities, under the VIPack™ platform.

Evolution of Chiplet Design

As the chiplet design approach accelerates, ASE’s advanced interconnect technology allows designers to consider innovative, high-density chiplet integration options. Normally, there are chip I/O density limitations for true 3D layered IP block considerations. Specifically, ASE’s microbump technology allows for a reduction in pitch from 40µm down to 20µm using a new metallurgical stack. Advances in microbump have extended the existing capabilities of silicon-to-silicon interconnect. However, this technology has helped to facilitate other development activities that allow even further pitch reductions.

When considering chiplets or IP block disaggregation of an SoC, there may be a high number of connections to interface with other areas of the design. This drives a higher number of connections that may be space-limited due to the small size of the IP block. Mainly, fine pitch interconnect capabilities enable a 3D integration capability and higher density for high I/O memory considerations.

AI Demands Advanced Interconnect Innovations

The global AI market is seen to grow exponentially throughout this decade. Therefore, ASE is delivering advanced interconnect innovations that meet complex chip design and system architecture requirements. It aims to lower overall manufacturing costs and enable faster time to market. Thus, the extended chip-level interconnect technology opens up more applications for chiplet consideration. Specifically, it targets high-end applications, like AI, and other key products such as mobile AP, microcontrollers, and more.

“Silicon-to-Silicon interconnect has moved from solder bump to microbump. As we move into the AI era, there’s growing need for further interconnect technology advancements that deliver enhanced reliability and optimized performance across a broad spectrum of nodes – and this is where ASE has stepped up,” commented Calvin Lee, Director of Corporate R&D, ASE. “We are breaking through barriers for chiplet integration through our new fine pitch interconnect capabilities. We will continue to push limits to meet dynamic chiplet integration requirements.”

“Our customers require transformative technologies that enable their product roadmaps, and advanced interconnect technologies such as micro bump, in combination with the VIPack structures, help to address performance, power, and latency challenges,” added Mark Gerber, ASE’s Senior Director of Engineering & Technical Marketing. “ASE’s advanced interconnect technologies present compelling options for customers that seek increasingly finer pitch solutions for overall performance improvement, scalability achievement, and power advantage.”

“We are pleased that ASE’s VIPack™ momentum continues through creative interconnect innovations that overcome limitations and align with dynamic application requirements,” added Yin Chang, Senior Vice President of Sales & Marketing at ASE. “At ASE, we empower our customers to explore and discover new performance and sustainable efficiencies in every single semiconductor design and system solution.”

ASE’s VIPack™ is a scalable platform that is expanding in alignment with industry roadmaps. It is supported by its Integrated Design Ecosystem™ (IDE), a collaborative design toolset optimized to systematically boost advanced package architecture.

-21 March 2024-