ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

Industry Leaders to Set Chiplet Interconnection Standards for Heterogeneous Computing

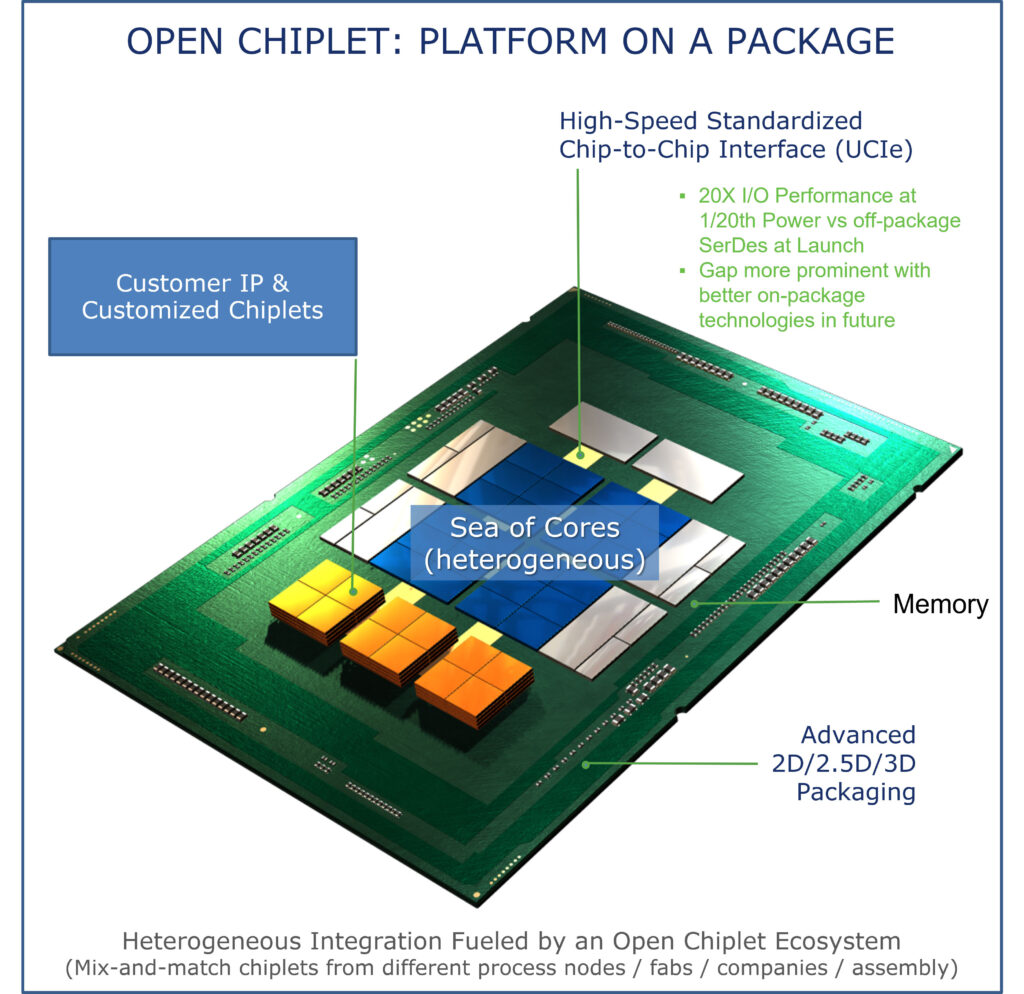

Major players in the global semiconductor manufacturing ecosystem have rallied behind an industrywide campaign to create a chiplet ecosystem for advanced 3D chip packaging standards as well as chip interconnection technologies.

The move is to keep up with growing complexity of chip architectures, as the industry is confronting ever toughest challenges in cramming more and more of different type of functional blocks into a given chip space. So, the industry is now turning to heterogeneous 3D chip packaging technologies that can allow it to integrate more of different chiplets into a package level, not silicon level.

Chiplet is a tiny integrated circuit that incorporates a well-defined subset of functionality. Heterogeneous integration is to integrate those chiplets of different nodes into an advanced 3D single package using as if Lego blocks are pieced together

The players plans to form an industry consortium to develop and set a standard for die-ti-die, or chiplet to chiplet interconnection technology, as the technology is a most crucial element in the heterogeneous integration package-level solution.

Topping the who’s who list of consortium members Advanced Semiconductor Engineering (ASE), AMD, ARM, Google Cloud, Intel Corp., Meta, Microsoft Corp., Qualcomm Inc., and TSMC, to just name a few.

The founding members suggested Universal Chiplet Interconnect Express or UCIe technology as an open industry standard for die-to-die interconnection technology. The s-called UCIe 1.0 specification includes die-to-die I/O physical layers, dit-to-die protocols, and software stack which leverages the well-established PCI Express and Compute Express Link industry standards.

The UCIe is an open specification that defines interconnection between chiplets within a package,

The specification will be available to the UCIe consortium members, which include foundries, system OEMs, silicon IP providers, IDMs, chip packaging companies and chip designers.

Once the consortium created later this year, member companies will work on a next generation of UCIe technologies, including chiplet form factors, management, enhanced security, and other essential protocols.