ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

Eliyan Sets New Standard for Chiplet Interconnect

Eliyan Corporation has announced the successful tape out of the industry’s highest performing PHY solution for multi-die architectures. Thus, the company achieved bandwidth of 64Gbps/bump on a 3nm process using standard packaging.

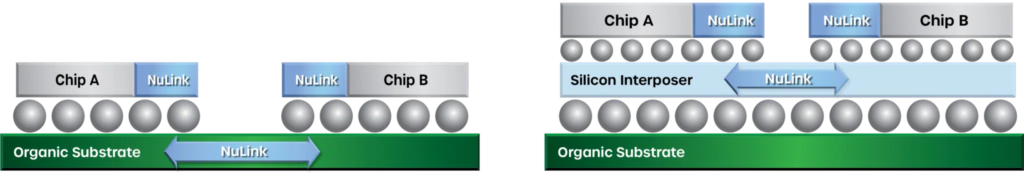

The milestone further confirms Eliyan’s ability to enable die-to-die connectivity on organic substrates while being compatible with emerging interconnect standards. Moreover, the process became possible with unprecedented power, area, and latency. Thus, eliminating the need for complex silicon interposers in most applications.

Compatible Multi-Die Solution

NuLink™ PHY is compatible with industry interconnect standards UCIe and BoW. Moreover, it also supports the UMI™ (Universal Memory Interconnect), a novel chiplet interconnect technology. particularly, this improves Die-to-Memory bandwidth efficiency by more than 2x. Furthermore, UMI leverages a dynamic bidirectional PHY whose specifications are currently being finalized at OCP/ODSA.

The first silicon of the company’s NuLink™ PHY in 3nm is likely to emerge in Q3 2024. Although the design will utilize standard organic/laminate packaging with 8-2-8 stack up, the highly area-efficient NuLink™ PHY has bump limitation and leverages innovative interference cancellation techniques to fit under not only 100um bump pitch of standard packaging, but also 55um of advanced packaging. In standard packaging it can deliver up to 4.55Tbps/mm and in advanced packaging can deliver up to 21Tbps/mm.

The successful tape-out demonstrates Eliyan’s technology in standard organic packaging. That is, achieving similar bandwidth, power efficiency, and latency as die-to-die implementations that others can only deliver using advanced packaging technologies.

In addition to allowing greater supply chain flexibility, the ability to implement chiplet-based systems in standard organic packages enables the creation of larger system-in-package (SiP) solutions. Thus, higher performance per power at considerably lower cost and system level power. These factors provide major gains in sustainability as well.

Address Business, Technical Challenges

The tape-out includes a die-to-die PHY coupled with an adaptor layer/link layer controller IP to provide complete solutions for customers. Thus, aligning with the high-growth AI markets for HPC and edge applications. Lower TCO accommodated by utilizing standard packaging can further encourage chiplet based designs in inference and gaming segments. In addition, to other adjacent markets as they can be more readily qualified for aerospace, automotive, and demanding industrial markets.

“Our strategy is to provide maximum flexibility in the choice of packaging options while delivering optimal performance required for any given application. While our support for advanced packaging techniques and the use of interposers offers significant benefits, there are practical considerations that make standard packaging a more viable choice in certain cases. By being able to deliver industry-leading bandwidth and maintain compatibility with emerging interconnect standards using organic substrates, we offer a best-of-both-worlds solution that addresses the business and technical challenges of any packaging alternative,” said Eliyan’s founding CEO Ramin Farjadrad.

Meanwhile, Raja Koduri, Founder and CEO of Mihira AI, noted, “Enabling ultra-high-bandwidth, low-power chiplet connectivity on larger-sized organic packages allows exciting options for architects. This will allow practical package construction to bring an efficient combination of compute density, memory bandwidth, and capacity, at a substantial improvement in performance-per-dollar and performance-per-watt.”