ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

Siemens, TSMC Partner on New Foundry Advancements

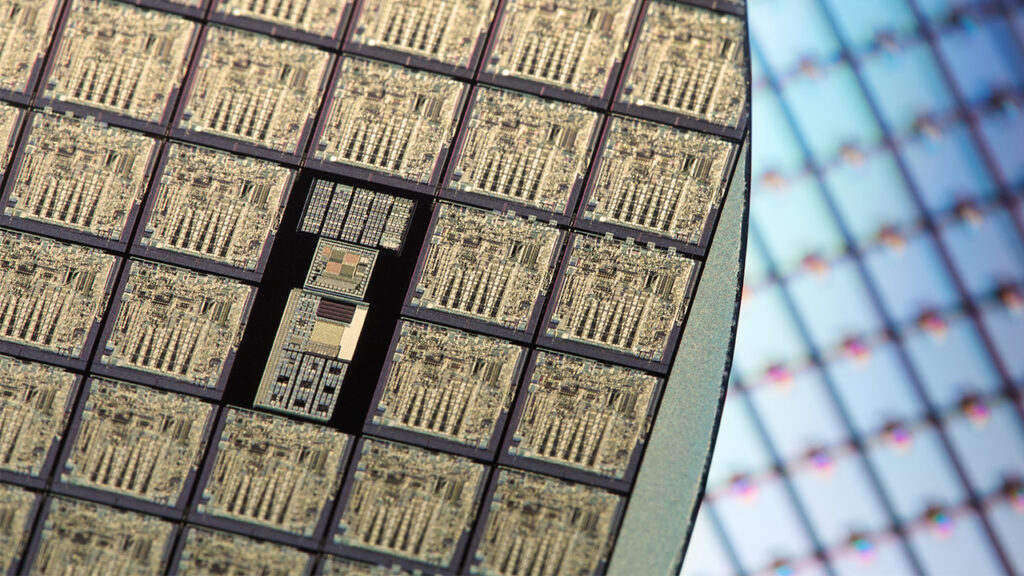

Siemens Digital Industries Software has announced new certifications and collaborations with longtime partner TSMC. Most importantly, the new alliance will result in multiple industry-leading Siemens EDA product lines for the foundry’s latest process technologies.

“TSMC’s collaboration with design ecosystem partners like Siemens helps our mutual customers remain at the forefront of technology innovation,” said Dan Kochpatcharin, head of the Design Infrastructure Management Division at TSMC.

Furthermore, Kochpatcharin said, “This close partnership provides customers with proven design solutions that allow customers to more fully leverage the significant performance and power efficiency advantages of TSMC’s advanced process technologies.”

Calibre Certified for TSMC’s N2 process

Siemens’ industry-leading Calibre® nmPlatform tool for integrated circuit (IC) verification sign-off has been fully certified for TSMC’s most advanced N2 process. This includes Calibre® nmDRC software, Calibre® YieldEnhancer™ software, Calibre® PERC™ software and Calibre® nmLVS software. Most importantly, all are now in place for the earliest adopters of this advanced new process technology offering from TSMC.

In addition, TSMC and Siemens have also collaborated to certify Siemens’ mPower™ analog software for transistor-level electromigration and IR drop (EM/IR) sign-off using TSMC’s N4P process. This achievement allows mutual customers to apply mPower’s unique EM/IR signoff solution to their next-generation analog or radio frequency (RF) designs.

Collaboration for Siemens’ Solido Design Environment, Analog FastSPICE

TSMC’s N4P, N3E and N2 custom design reference flow (CDRF) works now with Siemens’ Solido™ Design Environment software. Particularly, for advanced variation-aware verification at high sigma. In addition, Siemens’ Analog FastSPICE platform for circuit verification of nanometer analog, RF, mixed-signal, memory, and custom digital circuits has successfully achieved TSMC certification. This is for the foundry’s advanced N5A, N3E, N3P and N2 processes.

As part of the CDRF flow for TSMC’s N4P, N3E and N2 processes, Siemens’ Analog FastSPICE platform now supports TSMC’s Reliability Aware Simulation technology, which addresses IC aging and real-time self-heating effects among other advanced reliability features.

Investment in Place, Route continues with N3 Certifications for Aprisa

Reinforcing its strong commitment to investing in the digital implementation space, Siemens today announced yet another milestone for its Aprisa™ place and route solution with TSMC’s certification of the tool for the foundry’s N3E process. The N3E certification, together with Aprisa’s industry-leading ease-of-use, can help customers accelerate their migration to this node.

“TSMC’s pace of innovation is remarkable, and we are proud to work with this partner for the benefit of our many mutual customers,” said Joe Sawicki, executive vice president, IC-EDA for Siemens Digital Industries Software. “Optimizing our EDA solutions for TSMC’s latest processes helps us provide our mutual customers with innovative solutions that satisfy their challenging and rapidly evolving market and business requirements.”

TSMC Certifies Siemens’ Avanced 3DIC solutions

Siemens also announced it has made substantial progress with TSMC in certifying several of Siemens’ 3DIC solutions for TSMC’s advanced 3DFabric™ technologies. TSMC has certified 3Dblox 2.0 with Siemens’ Calibre® 3DSTACK software for physical analysis and circuit verification. This certification includes support for inter-chiplet DRC and LVS checks as requirements for TSMC 3DFabric technologies.

In addition, TSMC recently certified an array of Tessent™ 3DIC solutions including Tessent hierarchical DFT, Tessent Multi-die with enhanced TAPs (test access ports – IEEE 1838 compliant), native flexible parallel port (FPP) support using streaming scan network (SSN) and IEEE 1687 IJTAG network technologies.

Both partners are strengthening their commitments to investing in building 3DIC testing ecosystems under TSMC 3Dblox, which includes known good die (KGD) loopback test and physical aware die-to-die fault detection and diagnosis utilizing BMAP and PMAP standards.