ASIA ELECTRONICS INDUSTRYYOUR WINDOW TO SMART MANUFACTURING

Chip Makers to Reach New Design High With Siemens Tool

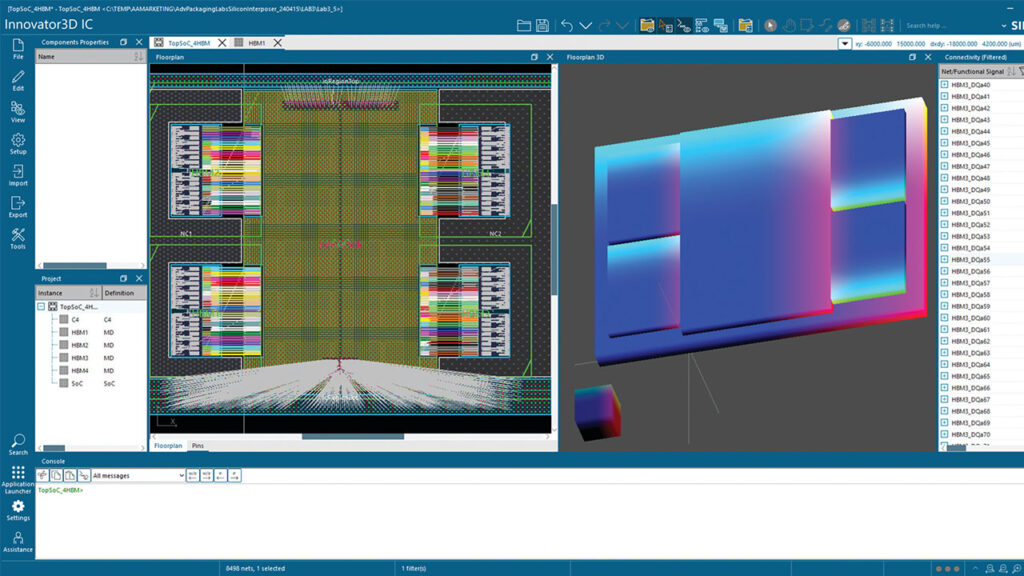

Siemens Digital Industries Software announced today Innovator3D IC™, new software that delivers a fast, predictable path. Specifically, for planning and heterogeneous integration of ASICs and chiplets using the latest and most advanced semiconductor packaging 2.5D & 3D technologies and substrates.

Siemens’ Innovator3D IC provides a consolidated cockpit for constructing a digital twin. Accordingly, it features a unified data model for design planning, prototyping, and predictive analysis. This cockpit drives implementation, multi-physics analysis, mechanical design, test, signoff, and release to manufacturing.

Comprehensive Portfolio

By unifying power, signal, thermal, and mechanical stress analysis tools, it enables rapid ‘what-if’ exploration. While at the same time, identifying, avoiding, and solving challenges prior to detailed design implementation. This shift-left approach can prevent costly and time-consuming downstream rework or suboptimal results.

“Siemens already had the most comprehensive portfolio of semiconductor packaging-related technologies available as part of Siemens Xcelerator,” said AJ Incorvaia, senior vice president of Electronic Board Systems at Siemens Digital Industries Software. In addition, Incorvaia said, “By combining these with Innovator3D IC we enable customers to achieve the realization of more-than-Moore.”

Innovator3D IC drives ASIC, chiplet and Interposer implementation. It uses Siemens’ Aprisa™ software digital IC place and route technology, Xpedition™ Package Designer software, Calibre® 3DThermal software, NX™ software for mechanical design, Tessent™ Test software, and Calibre® 3DSTACK software for interchiplet DRC, LVS and tapeout signoff.

Moreover, Innovator3D IC uses a hierarchical device planning approach to handle the massive complexity of advanced 2.5D/3D integrated designs with millions of pins. The designs’ representation comes as geometrically partitioned regions with attributes controlling elaboration and implementation methods. This allows quick implementation of critical updates while matching analytic techniques to specific regions. Thus, avoiding excessively long execution times. Hierarchical interface route path planning further optimizes chiplet interfaces and pin assignments.

Although Innovator3D IC is integrated with the Siemens Xcelerator portfolio of industry software, its open architecture also supports integration with third-party point solutions. Thus, a key tenant of Innovator3D IC is its support of industry standard formats, such as 3Dblox, LEF/DEF, Oasis, and interface IP protocols (such as UCIe and BoW).

Active participation in the Open Compute Projects Chiplet Design Exchange Working Group (OCP CDX) enables direct consumption of standardized chiplet models that will be provided by the emerging commercial chiplet ecosystem.

Comprehensive Verificaiton, Reliabliity

Innovator3D IC does not limit to 2.5D and 3D integrations. Accordingly, it is capable of planning and prototyping all leading and emerging semiconductor integration methodologies and platforms including interposers (organic, silicon or glass), ABF build-up, RDL based with chips first or last including support for Deca Technologies adaptive patterning process. It also suits Panel-Level-Packaging (PLP), embedded or raised silicon bridges as well as System-In-Package (SiP) and modules.

The Innovator3D IC solution comes architected around the System Technology Co-Optimization (STCO) methodology process developed by IMEC. In addition, it utilized throughout prototyping and planning, design, sign-off /manufacturing hand-off. Therefore, concluding with a comprehensive verification and reliability assessment.

Siemens developed Innovator3D IC using the Next Generation Electronics Systems Design (NGESD) AI-infused User eXperience (UX) technology. Specifically, it uses extensive multithreading and multicore capabilities to achieve optimal capacity and performance on 5+million pin designs.

“For advanced heterogeneous integration platforms such as EMIB, an integrated floorplanning and prototyping cockpit with predictive analysis is essential,” said Suk Lee, VP & GM of Ecosystem Technology Office, at Intel Foundry.

25 June 2024